# TMS32010 User's Citicle 1983

16/32-bit Digital Signal Processor

# TMS32010 USER'S GUIDE

# 16/32-BIT DIGITAL SIGNAL PROCESSOR

### **IMPORTANT NOTICE**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1983 Texas Instruments ISBN 0-904047-38-5

Edited by Paul Strzelecki, B.Sc.

| ARCHITECTURE                               | 2 |

|--------------------------------------------|---|

| INSTRUCTIONS                               | 3 |

| METHODOLOGY FOR APPLICATION DEVELOPMENT    | 4 |

| PROCESSOR RESOURCE MANAGEMENT              | 5 |

| INPUT/OUTPUT DESIGN TECHNIQUES             | 6 |

| MACRO LANGUAGE INSTRUCTIONS                | 7 |

| DIGITAL SIGNAL PROCESSING                  | 8 |

| DEVELOPMENT SUPPORT/PART ORDER INFORMATION | А |

INTRODUCTION

### **TABLE OF CONTENTS**

| SEC | TION  |                                                 | PAGE |

|-----|-------|-------------------------------------------------|------|

| 1.  | INTRO | ODUCTION                                        |      |

|     | 1.2   | Typical Applications                            | 1-1  |

|     | 1.3   | Key Features                                    | 1-2  |

|     | 1.4   | How To Use the TMS32010 Manual                  |      |

|     |       | 1.4.1 Glossary of Basic TMS32010 Hardware Terms |      |

|     |       | 1.4.2 References                                | 1-6  |

| 2.  | ΔRCH  | HITECTURE                                       | 2-1  |

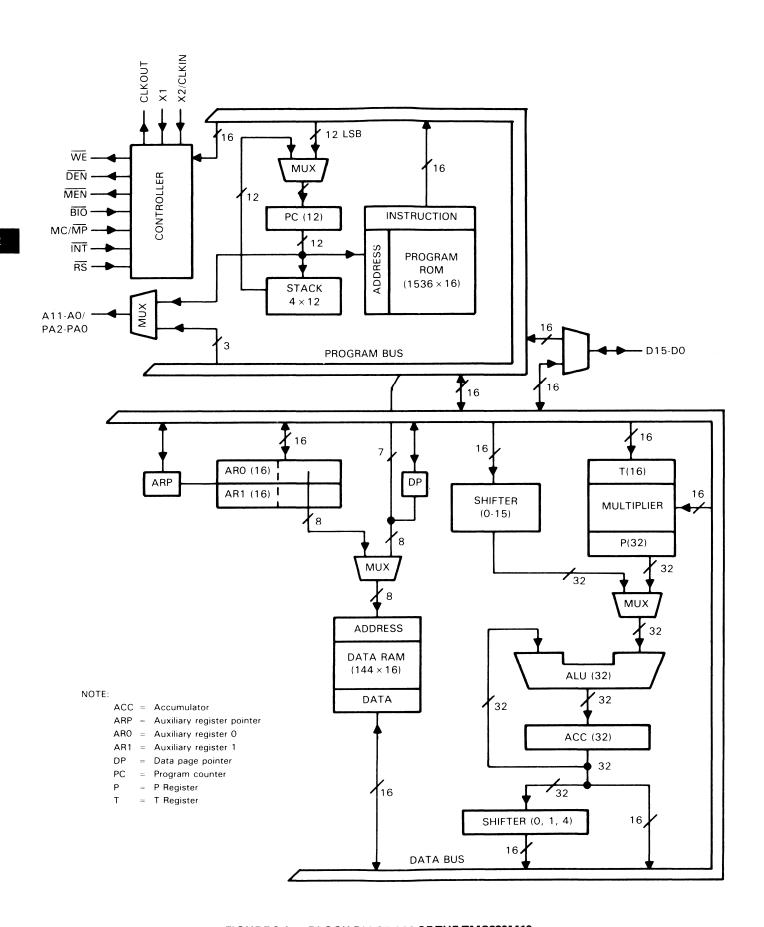

| ۷.  | 2.1   | Architectural Overview                          |      |

|     | 2.1   | 2.1.1 Harvard Architecture                      |      |

|     | 2.2   | Arithmetic Elements                             | _    |

|     | ۷.۷   | 2.2.1 ALU                                       |      |

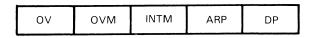

|     |       | 2.2.1.1 Overflow Mode (OVM)                     |      |

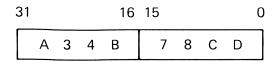

|     |       | 2.2.2 Accumulator                               |      |

|     |       | 2.2.2.1 Accumulator Status                      |      |

|     |       | 2.2.3 Multiplier                                |      |

|     |       | 2.2.4 Shifters                                  |      |

|     |       | 2.2.4.1 Barrel Shifter                          |      |

|     |       | 2.2.4.2 Parallel Shifter                        |      |

|     | 2.3   | Data Memory                                     |      |

|     | 2.0   | 2.3.1 Data Memory Addressing                    |      |

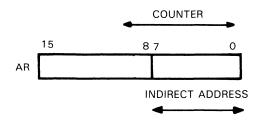

|     |       | 2.3.1.1 Indirect Addressing                     |      |

|     |       | 2.3.1.2 Direct Addressing                       |      |

|     | 2.4   | Registers                                       |      |

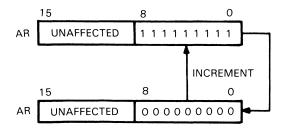

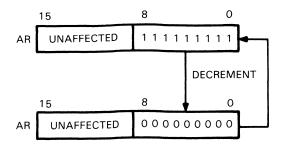

|     |       | 2.4.1 Auxiliary Registers                       |      |

|     |       | 2.4.2 Auxiliary Register Pointer                |      |

|     | 2.5   | Program Memory                                  |      |

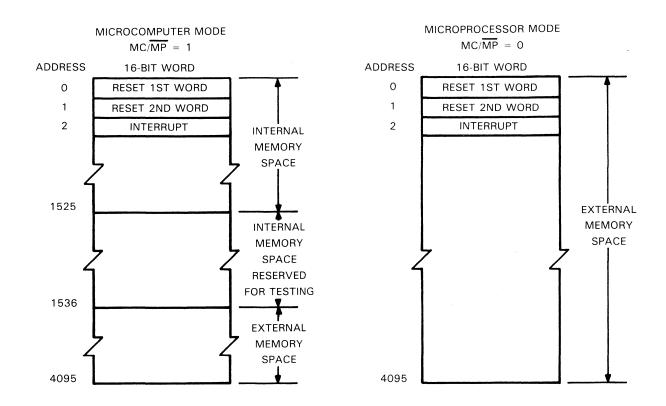

|     |       | 2.5.1 Modes of Operation                        |      |

|     |       | 2.5.1.1 Microcomputer Mode                      |      |

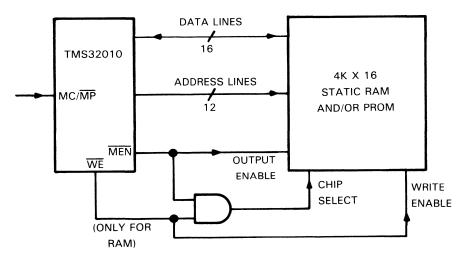

|     |       | 2.5.1.2 Microprocessor Mode                     |      |

|     |       | 2.5.2 Using External Program Memory             |      |

|     | 2.6   | Program Counter and Stack                       |      |

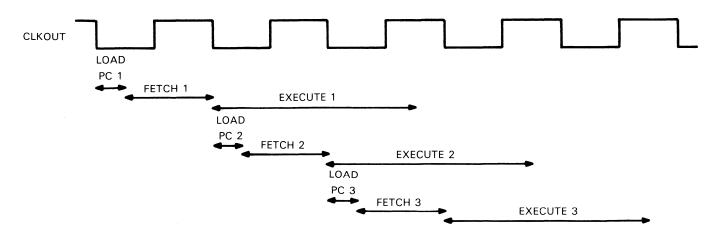

|     |       | 2.6.1 Program Counter                           |      |

|     |       | 2.6.2 Stack                                     |      |

|     |       | 2.6.2.1 Stack Overflow                          |      |

|     | 2.7   | Status Register                                 |      |

|     |       | 2.7.1 Saving Status Register                    |      |

|     | 2.8   | Input/Output Functions                          |      |

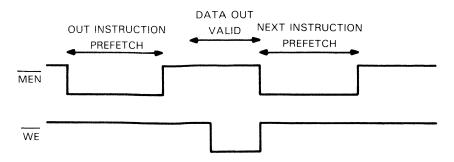

|     |       | 2.8.1 IN and OUT                                |      |

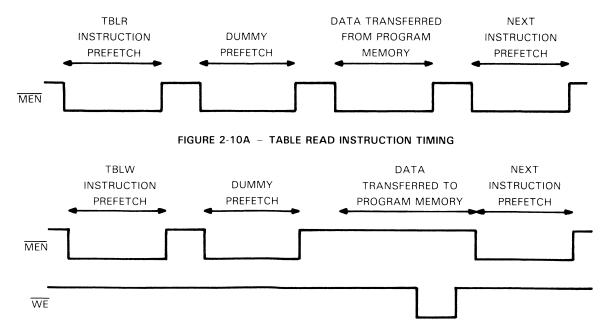

|     |       | 2.8.2 Table Read (TBLR) and Table Write (TBLW)  |      |

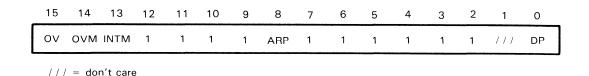

|     |       | 2.8.3 Address Bus Decoding                      |      |

|     | 2.9   | BIO Pin                                         | _    |

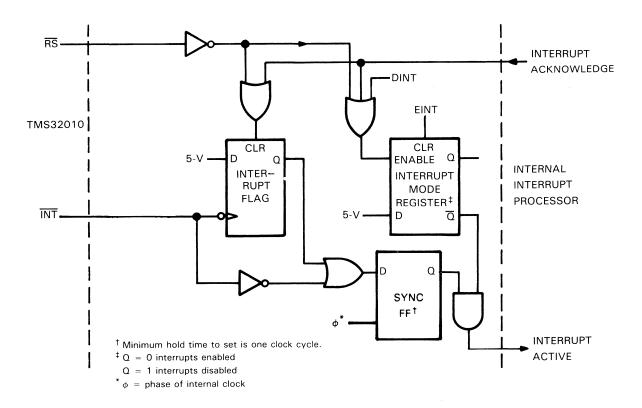

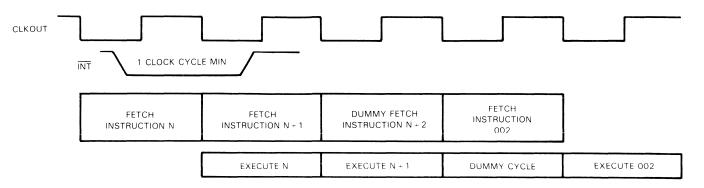

|     |       | Interrupts                                      |      |

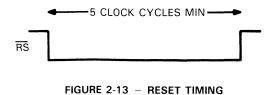

|     |       | Reset                                           |      |

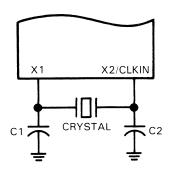

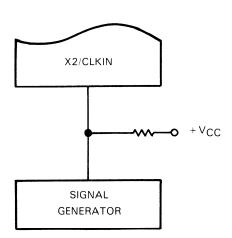

|     |       | Clock/Oscillator                                |      |

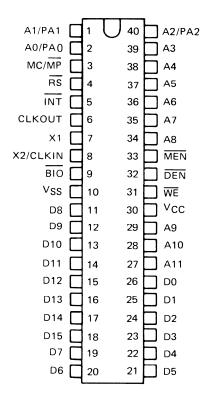

|     |       | Pin Descriptions                                |      |

|     |       |                                                 |      |

| 3. |     | RUCTIO  | DNS       |                |            |          |           |          |         |    | <br> |      |

|----|-----|---------|-----------|----------------|------------|----------|-----------|----------|---------|----|------|------|

|    | 3.1 | Introdu | uction    |                |            |          |           |          |         |    | <br> |      |

|    | 3.2 | Addres  | ssing Mo  | des            |            |          |           |          |         |    | <br> | 3-1  |

|    |     | 3.2.1   | Direct A  | ddressing M    | /lode      |          |           |          |         |    | <br> | 3-1  |

|    |     | 3.2.2   | Indirect  | Addressing     | Mode       |          |           |          |         |    | <br> | 3-1  |

|    |     | 3.2.3   | Immedia   | te Addressi    | ng Mode    |          |           |          |         |    | <br> | 3-2  |

|    | 3.3 | Instruc | ction Add | ressing Form   | mat        |          |           |          |         |    | <br> | 3-2  |

|    |     |         |           | ddressing F    |            |          |           |          |         |    |      |      |

|    |     |         |           | Addressing     |            |          |           |          |         |    |      |      |

|    |     |         |           | te Addressi    |            |          |           |          |         |    |      |      |

|    |     |         |           | s of Instruc   |            |          |           |          |         |    |      |      |

|    | 3.4 |         | •         |                |            |          |           |          |         |    |      |      |

|    | 0   | 3.4.1   |           | and Abbre      |            |          |           |          |         |    |      |      |

|    |     |         |           | on Set Sum     |            |          |           |          |         |    |      |      |

|    |     |         |           |                |            |          |           |          |         |    |      |      |

|    |     | 3.4.3   | mstructi  | on Descripti   | ions       |          |           |          |         |    | <br> | 3-0  |

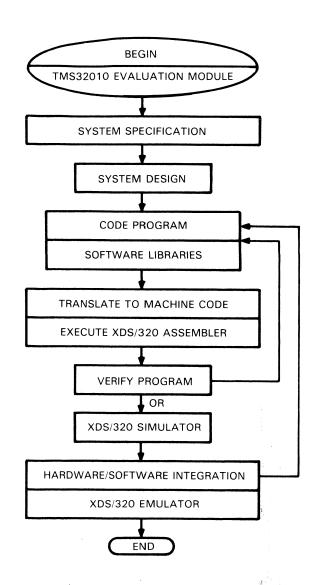

| 4. | MET | HODOL   | OGY FOR   | R APPLICAT     | ION DEVE   | OPME     | NT        |          |         |    |      | 4-1  |

| •• | 4.1 |         |           | elopment Pro   |            |          |           |          |         |    |      |      |

|    | 4.2 |         |           | Developmen     |            |          |           |          |         |    |      |      |

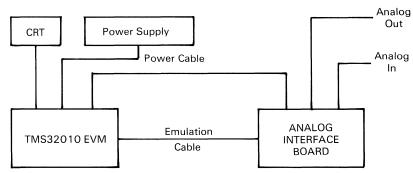

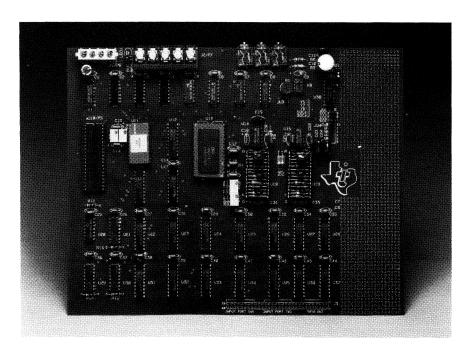

|    | 4.2 |         |           | )10 Evaluati   |            |          |           |          |         |    |      |      |

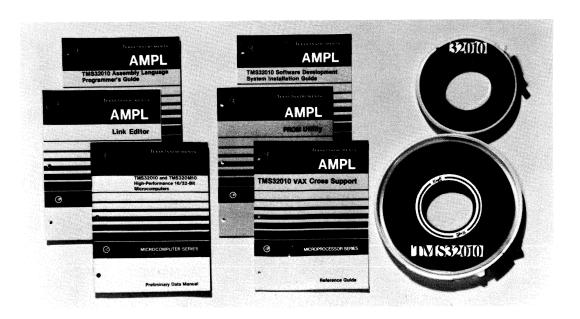

|    |     |         |           | O Macro As     |            |          |           |          |         |    |      |      |

|    |     |         |           |                |            |          |           |          |         |    |      |      |

|    |     |         |           | e Libraries .  |            |          |           |          |         |    |      |      |

|    |     |         |           | O Simulator    |            |          |           |          |         |    |      |      |

|    |     |         |           | D Emulator .   |            |          |           |          |         |    |      |      |

|    | 4.3 |         |           | elopment P     |            |          |           |          |         |    |      |      |

|    |     |         | -         | Specificatio   |            |          |           |          |         |    |      |      |

|    |     |         | •         | Design         |            |          |           |          |         |    |      |      |

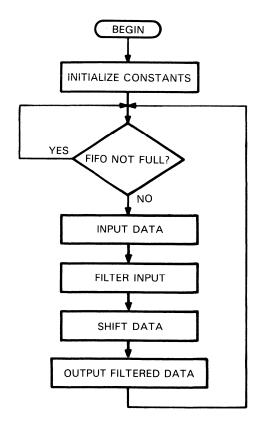

|    |     | 4.3.3   | Code De   | velopment .    |            |          |           |          |         |    |      |      |

|    |     |         | 4.3.3.1   | Discrete-Ti    | ime Filter | Flowcha  | irt       |          |         |    | <br> |      |

|    |     |         | 4.3.3.2   | FORTRAN        | Program.   |          |           |          |         |    | <br> | 4-5  |

|    |     |         | 4.3.3.3   | Assembly       | Language   | Progran  | n Using I | Relocata | ble Cod | le | <br> | 4-6  |

|    |     |         |           | 4.3.3.3.1      | Assembl    | er Outpu | ut        |          |         |    | <br> | 4-9  |

|    |     |         |           | 4.3.3.3.2      |            |          |           |          |         |    |      |      |

|    |     |         | 4.3.3.4   | Assembly       | _          | _        |           |          |         |    |      |      |

|    |     |         |           |                |            |          |           |          |         |    |      |      |

| 5. |     |         |           | RCE MANA       |            |          |           |          |         |    |      |      |

|    | 5.1 |         |           | perations      |            |          |           |          |         |    |      |      |

|    |     | 5.1.1   |           | pulation       |            |          |           |          |         |    |      |      |

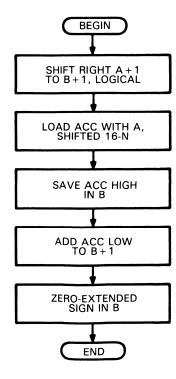

|    |     |         |           | ift            |            |          |           |          |         |    |      |      |

|    |     | 5.1.3   | Fixed-Po  | int Arithme    | tic        |          |           |          |         |    | <br> |      |

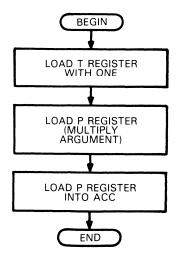

|    |     |         | 5.1.3.1   | Multiplicati   | ion        |          |           |          |         |    | <br> | 5-3  |

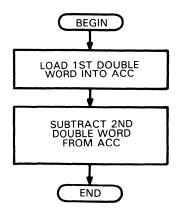

|    |     |         | 5.1.3.2   | Addition       |            |          |           |          |         |    | <br> | 5-5  |

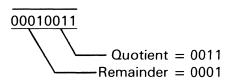

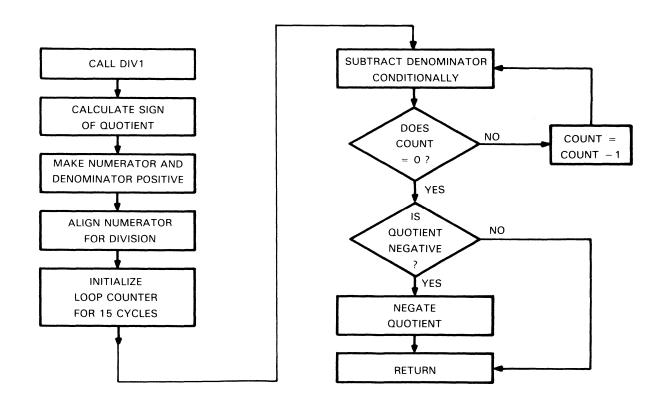

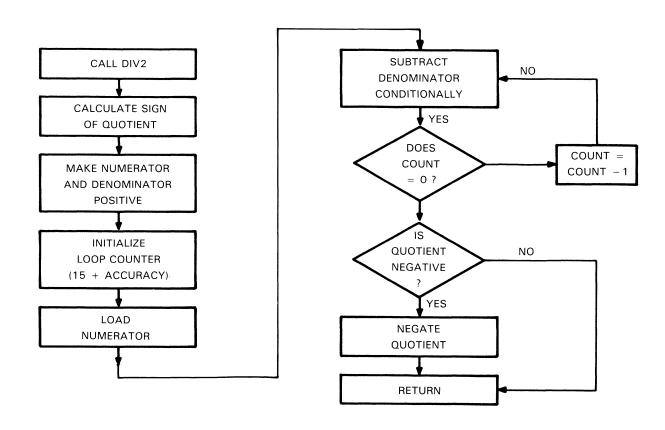

|    |     |         | 5.1.3.3   | Division       |            |          |           |          |         |    | <br> | 5-5  |

|    |     | 5.1.4   | Subrouti  | nes            |            |          |           |          |         |    | <br> | 5-11 |

|    |     | 5.1.5   | Compute   | ed GO TOs      |            |          |           |          | ,       |    | <br> | 5-12 |

|    | 5.2 | Addres  | ssing and | Loop Conti     | rol with A | uxiliary | Registers | 3        |         |    | <br> | 5-13 |

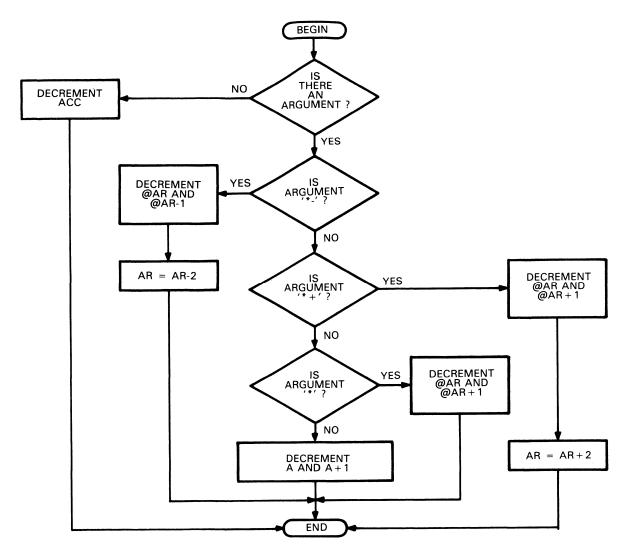

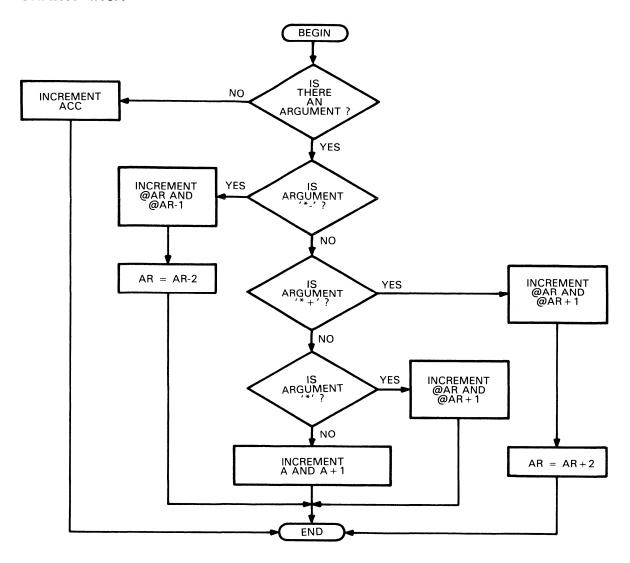

|    |     |         | •         | Register In    |            | •        | •         |          |         |    |      |      |

|    |     |         | ,         | unter          |            | _        |           |          |         |    |      |      |

|    |     |         |           | ition of Ope   |            |          |           |          |         |    |      |      |

|    | 5.3 |         |           | nd Convolut    |            |          |           |          |         |    |      |      |

|    | 0.0 | •       |           | Multiplication |            |          |           |          |         |    |      |      |

|    |     |         | •         | Data           |            |          |           |          |         |    |      |      |

|    |     |         |           | Register       |            |          |           |          |         |    |      |      |

|    |     | 0.0.0   |           |                |            |          |           |          |         |    | <br> |      |

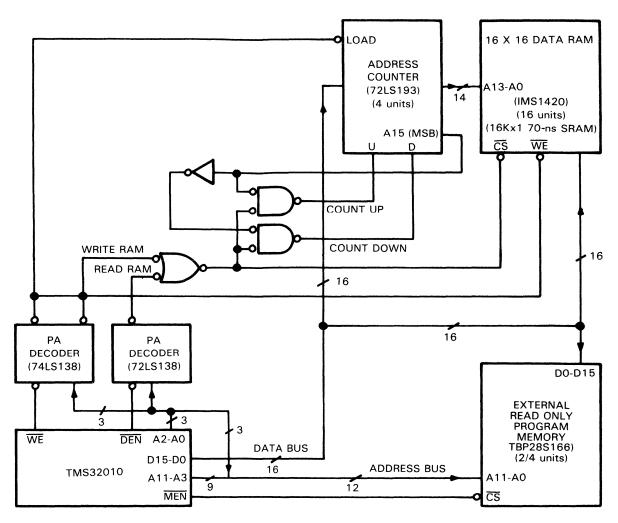

|    | 5.4    | Memory Considerations of Harvard Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -16        |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

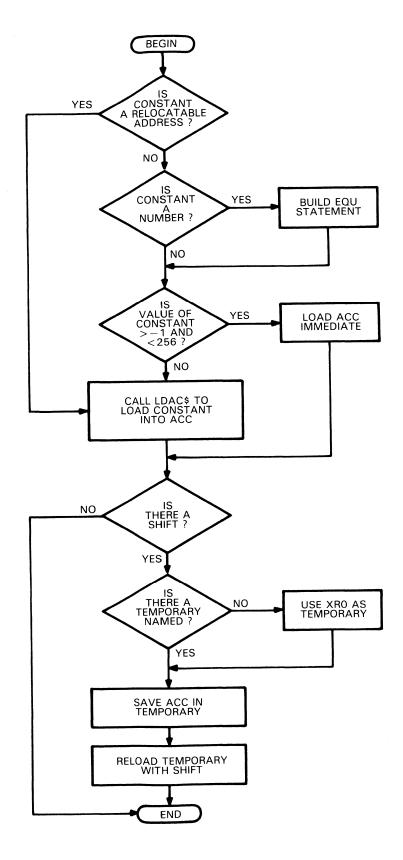

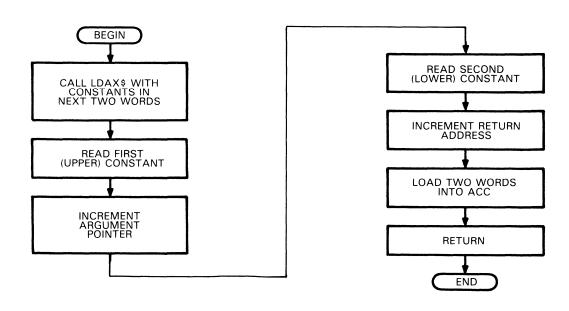

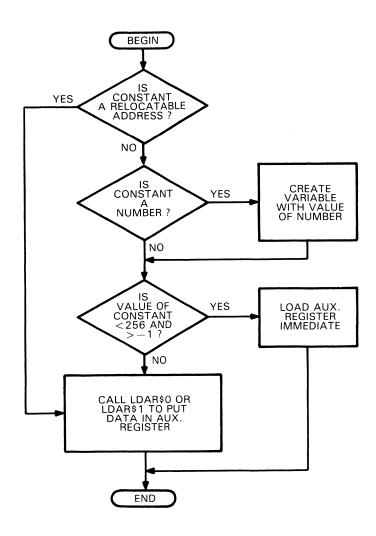

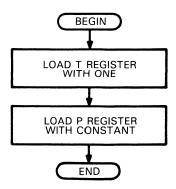

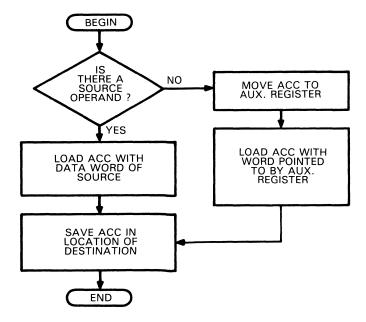

|    |        | 5.4.1 Moving Constants into Data Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -16        |

|    |        | 5.4.2 Data Memory Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -17        |

|    |        | 5.4.3 Program Memory Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -17        |

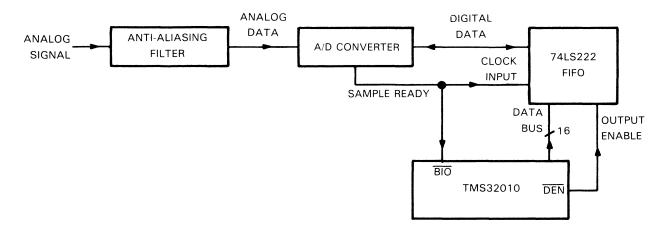

| 6. | INPLI  | T/OUTPUT DESIGN TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-1        |

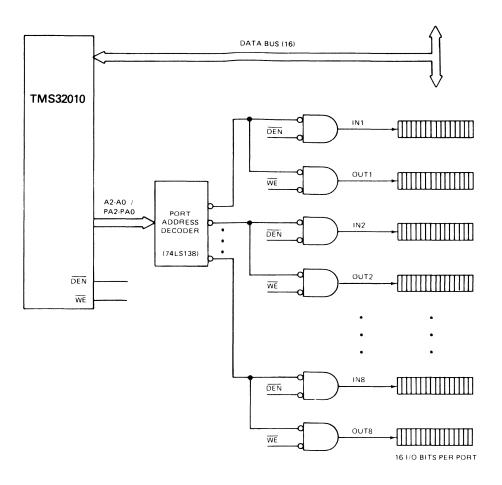

| Ο. | 6.1    | ,, • • · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-1        |

|    | 0.1    | 10.00.00.00.00.00.00.00.00.00.00.00.00.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-1        |

|    |        | or in the greatest and the second sec | 6-2        |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-2        |

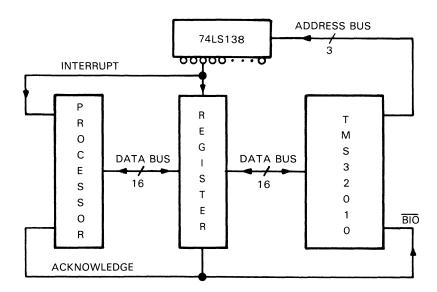

|    | 6.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-3        |

|    | 0.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-3        |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-4        |

| 7  | N4 A C | PRO LANGUA CE EVTENCIONO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-1        |

| 7. |        | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1<br>7-1 |

|    | 7.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|    | 7.2    | 11.00.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-2        |

|    | 7.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-6        |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-7        |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-22       |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-52       |

|    |        | 7.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-64       |

|    |        | 7.5.5 =59.54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-73       |

|    |        | 7.0.0 Zatonaou (2 odoro 11 oraș miles de mentre de la constitución de  | 7-97       |

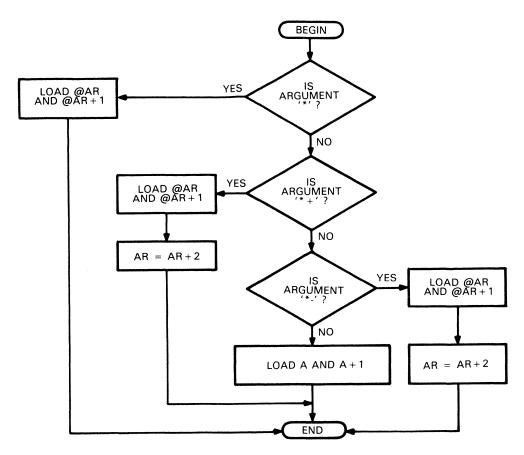

|    |        | 7.3.7 Load Array Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|    |        | 7.3.8 Special Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|    | 7.4    | Structured Programming Macros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|    | 7.5    | Utility Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 151        |

| 8. | DIGI   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-1        |

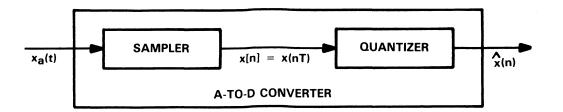

|    | 8.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-1        |

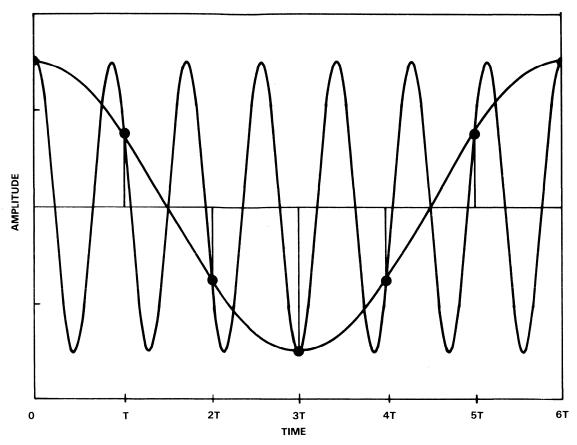

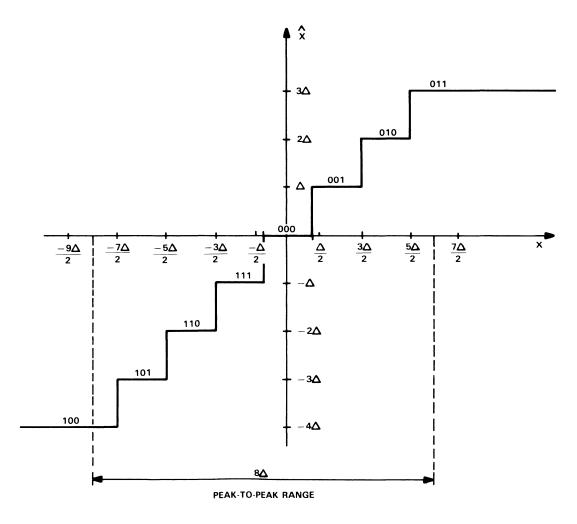

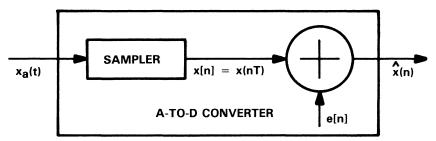

|    |        | • · · · · • • · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-2        |

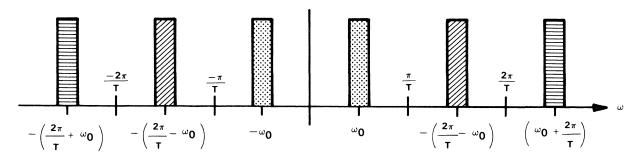

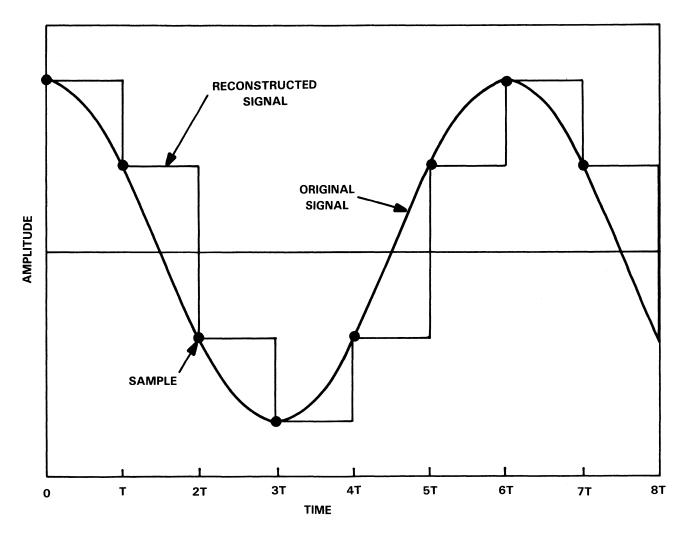

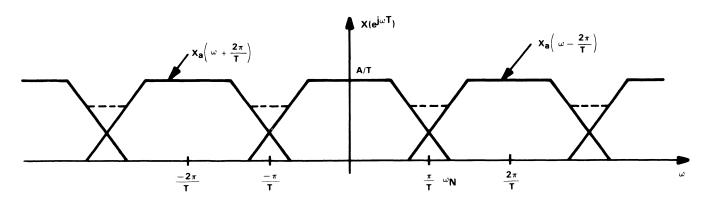

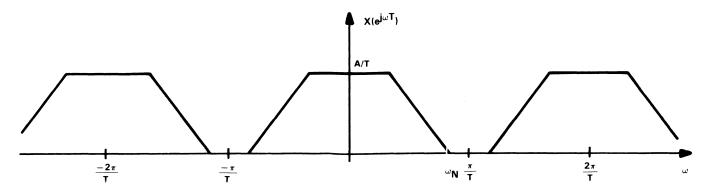

|    |        | errie eempre ====================================                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-5        |

|    | 8.2    | Basic Theory of Discrete Signals and Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8-6        |

|    |        | 8.2.1 Linear Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-6        |